概述

這款新型超低雜訊開關穩壓器具有超低雜訊、高效率、小尺寸和大電流等特點,非常適合雜訊敏感型射頻應用,包括 5G/無線、國防、儀器儀錶等。具有超低輸出雜訊的高級開關穩壓器系列被稱為 Silent Switcher® 3,在低頻範圍(0.1 Hz 至 100 kHz)內的雜訊甚至低於大多數低壓差 (LDO) 穩壓器。本文探討了與傳統的降壓 + LDO 穩壓器解決方案相比,在雜訊敏感型 RF 系統中應用超低雜訊開關穩壓器的挑戰和系統優勢。該研究基於射頻應用的兩個代表性案例研究:高性能鎖相環 (PLL) 時鐘和先進的高速 ADC 系統。通過適當的控制回路和濾波器設計,基於超低雜訊開關的新型單級解決方案為客戶節省了PCB空間和成本,並具有更小的解決方案尺寸、簡化的結構和更高的效率,同時仍支援出色的系統性能。

介紹

射頻系統對電源解決方案的雜訊性能提出了更嚴格的要求,這些解決方案用於各種應用,包括航空航太和國防、5G 無線應用、醫療設備、儀器儀錶等。確保電源解決方案的低輸出雜訊是保持卓越系統性能的關鍵方面之一。因此,雜訊敏感型 RF 應用的市場份額正在迅速擴大。傳統上,降壓 + LDO 穩壓器電源樹解決方案在這些雜訊敏感型應用中佔據主導地位。然而,隨著下一代產品中負載消耗的電流越來越高,buck + LDO 穩壓器方案成為系統瓶頸,由於 LDO 穩壓器的電流能力有限,方案尺寸大、方案成本高、損耗高。

近年來,超低雜訊開關穩壓器已開發出具有優異電磁干擾 (EMI) 性能和超低頻(LF,0.1 Hz 至 100 kHz)雜訊的開發。1,2,3 最先進的超低雜訊開關穩壓器的低頻雜訊可與市場上最好的超低雜訊 LDO 穩壓器相媲美。先進的超低雜訊開關穩壓器改變了雜訊敏感型應用的遊戲規則,可同時提供超低雜訊、高電流能力、高效率和小尺寸。

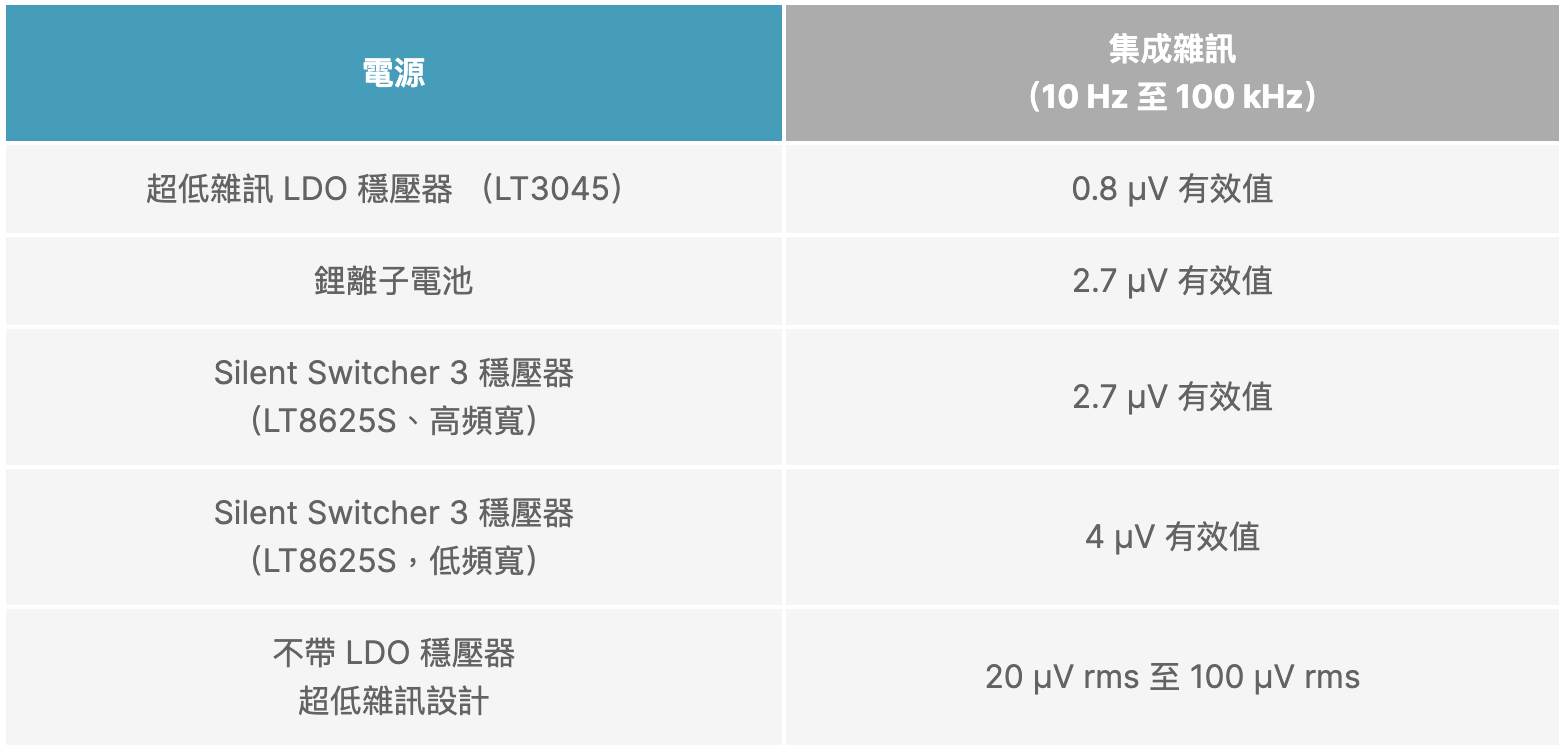

創新的超低雜訊開關穩壓器系列Silent Switcher3、在所有四個方面都具有行業領先的性能。1ADI 的 Silent Switcher 1 和 2 系列是開創性的開關穩壓器,具有高效率、低 EMI 雜訊和小尺寸解決方案,支援高達 65 V 的輸入電壓和高達 30 A 的輸出電流。Silent Switcher 3 技術基於成功的 Silent Switcher 1 和 2 技術,旨在高效提供比 LDO 穩壓器高得多的電流。 採用單個IC,可提供高達16 A的電流,採用4 mm×4 mm小型封裝。與 Silent Switcher 2 系列相比,Silent Switcher 3 系列採用創新的電路和結構設計,實現了超低頻輸出雜訊。1如表 1 所示,Silent Switcher 3 穩壓器在低頻範圍內的輸出雜訊低於沒有超低雜訊設計的 LDO 穩壓器。因此,基於單個超低雜訊開關穩壓器的單級電源解決方案在雜訊敏感型 RF 應用中取代傳統的降壓 + LDO 穩壓器解決方案方面極具競爭力。本文將通過幾個案例研究來介紹在雜訊敏感型應用中利用超低雜訊開關穩壓器 Silent Switcher 3 的卓越系統性能和系統優勢。此外,還將詳細介紹如何充分利用 Silent Switcher 3 穩壓器的卓越器件級性能,以實現所需的系統級性能。

採用超低雜訊開關穩壓器為 PLL 供電

RF 系統中的許多元件和系統對雜訊很敏感,例如 PLL、高速 ADC/DAC、混合信號前端 MxFE®等。特別是,高性能 PLL 是 RF 系統中最重要的元件之一,因為它提供 ADC、DAC、FPGA 和其他數位和混合信號 IC 所需的高質量時鐘信號。本節研究如何利用基於 Silent Switcher 3 技術的單級解決方案為高性能 PLL 供電並實現出色的 PLL 性能。這ADF4372,一種流行的額定頻率為5 GHz的高性能 PLL 頻率合成器被選中用於本研究。4圖 1 顯示了詳細的電源結構,以及用於實驗研究的演示板。

圖 1.(a) ADF4372 的詳細電源結構;(b) ADF4372 的演示板。

表 1.不同電源的輸出雜訊比較

在 RF 應用中,高性能 PLLs 的性能通過關鍵規格相位雜訊來評估。相位雜訊計算為 1 Hz 頻寬內的雜訊功率,根據主 RF 信號的功率進行歸一化,詳細定義如公式 1 所示。

因此,相位雜訊始終為負數,並且應盡可能低。相位雜訊的單位是 dBc/Hz,其中 c 表示它根據載波功率進行歸一化。如圖 1 所示,ADF4372 需要兩個電源軌,即 3.3 V 和 5 V,其中 5 V 是最敏感的電源軌,因為它為 PLL 內部的壓控振蕩器 (VCO) 供電。4在本案例研究中,3.3 V 始終由超低雜訊 LDO 穩壓器 (LT3045) 提供,而 5 V 由 Silent Switcher 3 穩壓器供電,以研究 Silent Switcher 3 穩壓器對 RF 輸出信號相位雜訊的影響。

圖 2 提供了 PLL 相位雜訊性能的基線評估,其 5 V 軌由基於 Silent Switcher 3 穩壓器 (LT8625S) 的單級解決方案供電。2基線評估使用 LT8625S 演示板進行,對 5 V 電源進行極小的更改。在這種情況下,ADF4372 仍然可以實現出色的相位雜訊,如圖 2 所示。從 10 Hz 到 100 kHz,測得的相位雜訊與 5 V 由超低雜訊 LDO 穩壓器供電的情況幾乎相同。然而,在 ~250 kHz 處存在尖峰,導致 100 kHz 至 500 kHz 的相位雜訊略高。~250 kHz 的相位雜訊尖峰是由 Silent Switcher 3 穩壓器的輸出雜訊引起的,該穩壓器在該頻率範圍內也處於穩定狀態。Silent Switcher 3穩壓器的輸出雜訊傳播到輸出RF信號的相位雜訊,因為VCO輸出對其電源雜訊高度敏感。

圖 2.超低雜訊 LDO 穩壓器 (LT3045) 和 Silent Switcher 3 穩壓器 (LT8625S) 在 5 V 電壓下的相位雜訊基準比較。

Silent Switcher 3 穩壓器的輸出雜訊尖峰是由低控制環路增益 (~0 dB) 引起的,該增益太弱,無法降低此頻率範圍內的輸出雜訊。該機制在數據表Silent Switcher 3 系列。2因此,可以通過調整補償來增加 Silent Switcher 3 穩壓器的控制頻寬,從而降低雜訊尖峰。因此,通過優化 Silent Switcher 3 穩壓器的控制環路以獲得更高的控制頻寬,可以進一步降低相位雜訊,如圖 3 所示。圖 2 中的基線相位雜訊評估結果是使用 Silent Switcher 3 穩壓器獲得的,該穩壓器具有慢速補償和低控制頻寬。通過優化控制環路並實現高頻寬,~250 kHz 的相位雜訊尖峰幾乎被消除,降低了 10 dBc/Hz 以上。儘管如此,基於 Silent Switcher 3 穩壓器的單級解決方案的相位雜訊略高於具有 100 kHz 至 500 kHz 超低雜訊 LDO 的 2 級解決方案。

圖 3.Silent Switcher 3 穩壓器控制頻寬對高性能 PLL 相位雜訊的影響

為了進一步增強由 Silent Switcher 3 穩壓器供電的相位雜訊性能,可以設計一個次級(第二個)LC 濾波器,並將其添加到 Silent Switcher 3 穩壓器的輸出中。圖 4 顯示了詳細的電路圖,以說明基於 Silent Switcher 3 穩壓器的單級解決方案,其中第二個 LC 濾波器用於為 5 V 電源軌供電。使用第二個 LC 濾波器,可以從本地輸出或第二個 LC 濾波器之後的遠端輸出側感應輸出電壓。在這種情況下,選擇本地輸出進行輸出電壓感應,以簡化控制回路設計。由於高性能 PLL 消耗的電流較低(通常低於 1 A),因此第二個 LC 濾波器兩端的壓降很小,因此僅感應本地輸出電壓是合理的。因此,選擇本地輸出電容以保證 Silent Switcher 3 穩壓器的穩定運行。然後,一般設計指南建議遠端輸出電容應高於本地輸出電容,以降低系統穩定性對負載電容的敏感度。5。

圖 4.Silent Switcher 3 穩壓器的電路圖,帶有第二個 LC 濾波器,為 PLL 提供 5 V。

確定本地和遠端輸出電容後,可以根據截止頻率或第二個 LC 濾波器的諧振頻率選擇第二個電感 L2。根據圖 3,設計目標是在 250 kHz 時實現 >10 dBc/Hz 的衰減,這需要第二個 LC 濾波器在 250 kHz 時產生至少 20 dB 的衰減。250 kHz 時 30 dB 衰減用於提供更高的裕量,因此第二個 LC 濾波器(衰減為 –40 dB/dec)的截止頻率應為 44.6 kHz。因此,第二個 LC 濾波器的計算電感為 260 nH。最終電感選擇為 330 nH,並考慮了電感容差(通常為 ±20%)。最後但並非最不重要的一點是,在第二個 LC 濾波器設計中應實現足夠的阻尼,其中設計經驗法則是品質因數 Q 應低於 1。5因此,增加了 120 mΩ 的阻尼電阻,並與遠端輸出電容器串聯,導致有效 Q 值為 0.7。

Silent Switcher 3 解決方案配備了圖 4 中設計的第二個 LC 濾波器,其相位雜訊性能與具有超低雜訊 LDO 穩壓器的 2 級解決方案幾乎相同。如圖 5 所示,設計的第二個 LC 濾波器進一步提高了由 Silent Switcher 3 穩壓器驅動的相位雜訊性能,從而在 10 Hz 至 10 MHz 範圍內獲得與超低雜訊 LDO 穩壓器幾乎相同的結果。儘管由於 Silent Switcher 3 穩壓器的開關頻率,由 Silent Switcher 3 穩壓器供電的相位雜訊結果在 2 MHz 處仍然有一個小雜散,但小雜散具有遠離載波頻率的可預測頻率,因此不難解決。

圖 5.超低雜訊 LDO 穩壓器 (LT3045) 和 Silent Switcher 3 穩壓器 (LT8625S) 與第二個 LC 濾波器的 5 V ADF4372相位雜訊比較。

此外,無論是否設計了第二個 LC 濾波器,Silent Switcher 3 解決方案支援的相位雜訊都比 Silent Switcher 2 穩壓器 (LTM8024) 和其他供應商的常規開關穩壓器低得多。如圖 6a 所示,作為一款超低雜訊降壓型開關穩壓器,與 Silent Switcher 2 穩壓器和常規開關穩壓器相比,Silent Switcher 3 穩壓器在 1 kHz 至 500 kHz 範圍內的相位雜訊要低得多。在 <1 kHz 時,由不同電源供電的測得相位雜訊沒有差異。這是因為在如此低的頻率下,高性能 PLL 的相位雜訊由 PLL 的參考時鐘主導,而不是其電源。此外,Silent Switcher 3 穩壓器可以實現比 LDO 穩壓器更低的相位雜訊,而無需特殊的超低雜訊設計,如圖 6b 所示。相位雜訊差異為 >在 5 kHz 至 100 kHz 範圍內為 10 dBc/Hz,其中 Silent Switcher 3 穩壓器在輸出雜訊方面優於沒有超低雜訊設計的 LDO 穩壓器(如表 1 所示)。總之,通過適當的控制環路和濾波器設計,基於 Silent Switcher 3 穩壓器的單級解決方案可以支援與具有超低雜訊 LDO 穩壓器的 2 級解決方案幾乎相同的 PLL 性能。與採用 LDO 穩壓器且無超低雜訊設計的 2 級解決方案相比,基於 Silent Switcher 3 的單級解決方案可實現更好的 PLL 相位雜訊。

圖 6.不同電源下 PLL 時鐘 (ADF4372) 的相位雜訊:(a) ADF4372 的相位雜訊(5 GHz 輸出);(b) ADF4372的相位雜訊(5 GHz 輸出)。

利用超低雜訊開關穩壓器為 ADC 系統供電

本節重點介紹利用基於 Silent Switcher 3 穩壓器的單級電源解決方案的 ADC 系統優勢。ADC 系統廣泛用於眾多射頻應用,例如 5G/無線、國防等。ADC 系統通常由 PLL clock、ADC 和數位處理器組成。在本案例研究中,選擇了高級高速 ADC,AD9208帶寬為 9 GHz。6ADF4372 演示板仍然用於為系統提供 clock 信號。生成模擬信號(1.23 GHz,幅度為 –10 dBFS)作為 ADC 的輸入信號。在數位側,使用高速 FPGA 板(ADS7-V2EBZ 板)和 ACE 軟體來檢查數位信號並評估 ADC 性能。ADC 系統的詳細資訊如圖 7 所示。

圖 7.正在研究的先進 ADC 系統的詳細結構。

本 ADC 案例研究的第一部分研究了 ADC 系統性能和 Silent Switcher 3 穩壓器作為 PLL 時鐘電源的優勢。同樣,ADF4372的 3.3 V 電源軌始終來自超低雜訊 LDO 穩壓器 (LT3045),而 5 V 電源軌則由 Silent Switcher 3 解決方案或其他電源解決方案提供。此外,AD9208 始終由標準展示板上安裝的預設電源解決方案供電。在相同的類比輸入信號下,圖 8 顯示了在不同 PLL 時鐘電源下,頻率跨度為 2 MHz 的 ADC 輸出信號在 1.23 GHz 附近的平均快速傅里葉變換 (FFT) 結果。與其他開關穩壓器相比,Silent Switcher 3穩壓器可實現最佳ADC性能,在1.23 GHz附近具有最低雜訊,但其FFT波形在~250 kHz頻率偏移處仍處於穩定狀態。

圖 8.ADC 採樣時鐘(超低雜訊 LDO 穩壓器、Silent Switcher 3 穩壓器、Silent Switcher 2 穩壓器和常規開關穩壓器)在不同電源下 ADC 輸出信號的平均 FFT 結果。

ADC 系統性能對其採樣時鐘信號的品質(即相位雜訊)很敏感。~250 kHz 的這個平台與ADF4372輸出信號的相位雜訊圖中相同頻率的小尖峰非常吻合(圖 3 中的綠色曲線)。正如 PLL 案例研究所揭示的那樣,可以通過添加 filter 來消除 phase noise 圖中的這個小雜散。因此,可以通過添加第二個 LC 濾波器來提高 Silent Switcher 3 穩壓器作為時鐘電源實現的 ADC 性能,實驗結果對此有很好的支援。圖 9 顯示了 Silent Switcher 3 解決方案下 ADC 輸出的 FFT 結果,圖 4 中採用第二種 LC 濾波器設計。ADC 輸出的最終輸出 FFT 波形在主 1.23 GHz 信號附近具有極低的雜訊,這與超低雜訊 LDO 穩壓器的結果幾乎相同。毫不奇怪,圖 9 還顯示,在設計了第二個 LC 濾波器的情況下,Silent Switcher 3 穩壓器在 <100 kHz 頻率偏移下,其 FFT 結果優於在沒有超低雜訊設計的 LDO 穩壓器下,因為它的 LF 雜訊較低,並且產生的 PLL 時鐘信號具有較低的相位雜訊。

圖 9.ADC 採樣時鐘(帶第二個 LC 濾波器的 Silent Switcher 3 穩壓器,無超低雜訊設計的 LDO 穩壓器)在不同電源下 ADC 輸出信號的平均 FFT 結果。

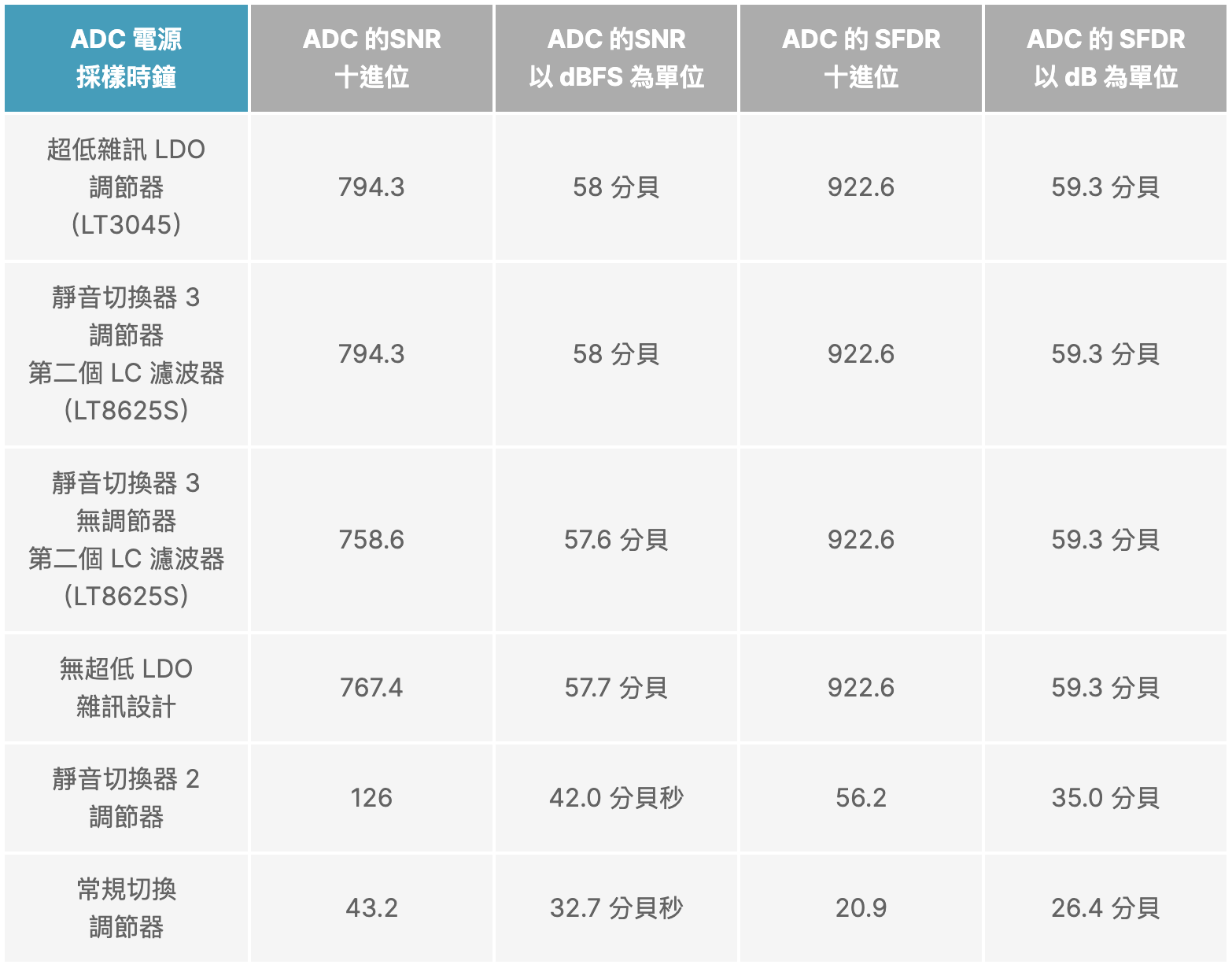

除了 ADC 輸出的 FFT 結果外,還評估了兩個重要的 ADC 參數,即信噪比 (SNR) 和無雜散動態範圍 (SFDR),以更全面地評估 ADC 系統性能。6 SNR 的定義很簡單;而 SFDR 定義為輸入信號的 rms 幅度與任何雜散雜訊信號的最高 rms 幅度之比。SNR 和 SFDR 的計算不是在輸入信號頻率附近使用窄頻率跨度,而是考慮了寬頻率範圍內的雜訊。如表2所示,Silent Switcher 3解決方案無需任何LDO後置穩壓器,其SNR和SFDR與採用超低雜訊LDO穩壓器的傳統兩級解決方案支援的SNR和SFDR相同。第二個 LC 濾波器對測得的 SNR 和 SFDR 影響很小。此外,與其他開關穩壓器解決方案相比,Silent Switcher 3 解決方案的 SNR 和 SFDR 要高得多:~20× SNR(十進位)和 ~45× SFDR(十進位)是由常規開關穩壓器引起的。與沒有超低雜訊設計的 LDO 穩壓器相比,Silent Switcher 3 解決方案的 SNR 略好,SFDR 相同,因為它的優勢僅在於輸入頻率附近的雜訊,只佔用於 SNR 計算的雜訊的一小部分。

表 2.AD9208 在不同電源下 ADC 採樣時鐘的 SNR 和 SFDR 比較

本案例研究的另一個方面是探討使用 Silent Switcher 3 穩壓器為 ADC 供電時的 ADC 系統性能和優勢。在這部分, PLL 時鐘始終由預設的 2 級解決方案和超低雜訊 LDO 穩壓器 (LT3045) 供電,以專注於 ADC 電源的影響。特別是,選擇AD9208的類比軌AVDD1作為範例,以簡化研究。0.975 V AVDD1 軌佔總功率的 19%,消耗 640 mA 標稱電流,併為時鐘域供電。6它對電源雜訊敏感,因此根據理論和實證分析進行選擇。所有其他電源軌仍由標準展示板上安裝的預設電源解決方案供電。

實驗結果表明,單級 Silent Switcher 3 解決方案可以替代傳統的 2 級解決方案為 ADC 供電,而不會影響 ADC 性能。對 ADC 輸出的平均 FFT 結果進行全面分析,以 Silent Switcher 3 解決方案 (LT8625S) 作為 AVDD1 評估 ADC 性能。需要注意的是,未安裝第二個 LC 濾光片。如圖 10 所示,使用 Silent Switcher 3 穩壓器為 AVDD1 供電時,ADC 輸出的 FFT 結果幾乎是理想的,與 2 級解決方案(降壓 + 超低雜訊 LDO 穩壓器)中 AVDD1 的 FFT 結果一樣令人滿意。即使未安裝第二個 LC 濾波器,在 ~250 kHz 頻率偏移處也沒有尖峰。

圖 10.提供 AVDD1 的不同電源(超低雜訊 LDO 穩壓器、Silent Switcher 3 穩壓器、Silent Switcher 2 穩壓器和常規開關穩壓器)下 ADC 輸出信號的平均 FFT 結果。

此外,ADC 性能對 ADC 電源的低頻雜訊不是很敏感。相反,它的性能對 ADC 電源的開關紋波更敏感。在 2 MHz 開關頻率下,基於 Silent Switcher 2 穩壓器的單級解決方案也導致了接近基頻 (1.23 GHz) 的近乎理想的 ADC 輸出波形,儘管 Silent Switcher 2 穩壓器沒有優化的低頻雜訊性能。這是因為基頻附近的 ADC 輸出雜訊由其採樣時鐘的相位雜訊主導,如本案例研究的第一部分所示。換句話說,接近基頻的高速 ADC 的輸出雜訊對 ADC 電源雜訊不是很敏感。儘管如此,使用 LF 雜訊過高的常規開關穩壓器(如 AVDD1)將使 ADC 輸出雜訊在基頻附近變得更糟,如圖 10 所示。圖 10 還顯示,ADC 電源的開關紋波將傳播到 ADC 輸出,導致 ADC 輸出的 FFT 結果出現相當大的雜散。例如,開關頻率為 750 kHz 的常規開關穩壓器作為 AVDD1,在 750 kHz 頻率偏移處會產生 >30 dB 的雜散。先前研究開關紋波雜訊對高速數據轉換器(ADC 和 DAC)性能影響的文獻也很好地支援了這一點。7, 8因此,通過適當的濾波器設計,基於 Silent Switcher 3 技術的單級解決方案完全可以滿足 ADC 的電源要求並支援令人滿意的性能。

總之,基於 Silent Switcher 3 技術的單級電源解決方案可以用超低雜訊 LDO 穩壓器取代傳統的 2 級解決方案,為高級 ADC 系統中的 PLL 時鐘和高速 ADC 供電。基於 Silent Switcher 3 技術的單級解決方案仍然可以支援令人滿意的 ADC 系統性能,與傳統的降壓 + LDO 穩壓器解決方案相比,關鍵 ADC 參數(包括 SNR、SFDR、雜訊性能等)不受影響。此外,與自身的電源雜訊相比,ADC 性能對其採樣時鐘源的電源雜訊更敏感。因此,Silent Switcher 3 技術需要適當的控制環路和輸出濾波器設計,才能為高級 ADC 系統提供令人滿意的系統性能,尤其是其 PLL 時鐘。

用於 ADC 系統的基於超低雜訊開關穩壓器的電源樹

前面的部分已經證明,Silent Switcher 3 技術非常適合為高級 ADC 系統的高性能 PLL 和高速 ADC 供電。Silent Switcher 3 技術能夠滿足高級 ADC 系統的電源要求,而不會影響系統性能。因此,可以為 ADC 系統設計一個全新的簡化電源樹,無需任何 LDO 穩壓器,它完全基於 Silent Switcher 3 IC。換句話說,傳統的 2 級解決方案(降壓 + LDO 穩壓器)完全被基於超低雜訊開關穩壓器 Silent Switcher 3 的單級解決方案所取代。基於上一節的ADC系統案例研究,圖11比較了ADC系統的原始電源樹(ADF4372 + AD9208)和基於Silent Switcher 3技術的新簡化電源樹。原始電源樹結構基於AD9208和 ADF4372標準演示板中使用的電源解決方案;而新的電源樹是基於最新的 Silent Switcher 3 器件設計的,適用於低電流應用(LT8622S和LT8624S).

圖 11.ADC 系統的新舊電源樹比較 (AD9208 + ADF4372):(a) 原始電源樹(2 級降壓 + LDO 穩壓器解決方案);(b) 新的電源樹(基於 Silent Switcher 3 技術的單級解決方案)。

無需任何 LDO 穩壓器,新的電源樹即可實現顯著而全面的系統優勢。如圖 11 所示,基於 Silent Switcher 3 技術的電源樹是一個簡化的結構,只有 5 個 Silent Switcher 3 IC,而原來的電源樹需要 2 個開關穩壓器和 6 個 LDO 穩壓器。因此,新的電源樹可以節省大量的PCB面積和成本。此外,新的電源樹結構可以大幅提高效率,效率從 61.7% 提高到 84.8%。總功率損耗降低了 71%,從 3.919 W 降低到 1.136 W。傳統功率樹結構的 LDO 穩壓器級本身消耗 2.305 W 的功率損耗。總功率損耗的顯著降低不僅歸功於無需 LDO 穩壓器,還歸功於 Silent Switcher 3 IC 的高效率,即使在 2 MHz 開關頻率下也是如此。未來專為 <1 A 應用開發的超低雜訊開關穩壓器可以進一步提高基於 Silent Switcher 3 技術的電源樹的效率。

結論

超低雜訊開關穩壓器可在寬頻率範圍內實現超低輸出雜訊,並且仍然具有高效率和輸出電流能力。憑藉突破性的雜訊性能,ADI 的 Silent Switcher 3 技術甚至具有比大多數 LDO 穩壓器更低的低頻雜訊。因此,基於 Silent Switcher 3 技術的單級電源解決方案對於雜訊敏感型 RF 應用具有吸引力和前景。本文全面展示了 Silent Switcher 3 系列在雜訊敏感型 RF 應用中的優勢。兩個案例研究成功證明,基於Silent Switcher 3 技術的單級電源解決方案可以用超低雜訊 LDO 穩壓器取代傳統的 2 級解決方案,並且仍然支援不折不扣的系統性能。

在為高性能 PLL 時鐘供電時,Silent Switcher 3 技術可以實現與具有超低雜訊 LDO 穩壓器的 2 級解決方案幾乎相同的相位雜訊。Silent Switcher 3 技術甚至優於基於典型 LDO 穩壓器的 2 級解決方案,而 PLL 性能沒有超低雜訊設計。在 ADC 系統的另一個案例研究中,Silent Switcher 3 技術通過適當的濾波器設計可以實現卓越的 ADC 性能,關鍵 ADC 參數幾乎與降壓 + 超低雜訊 LDO 穩壓器解決方案相同。因此,可以為 ADC 系統開發基於 Silent Switcher 3 技術的簡化電源樹結構,而無需任何 LDO 穩壓器。與原來的降壓 + LDO 穩壓器解決方案相比,沒有任何 LDO 穩壓器的 Silent Switcher 3 解決方案不僅具有更少的元件和更小的解決方案尺寸,而且還將功率損耗降低了 71%。

引用

1“Silent Switcher 技術.“ Analog Devices, Inc.,2023 年。

2"LT8625S:具有超低雜訊基準的 18V/8A 降壓型 Silent Switcher 3.”Analog Devices, Inc.,2023 年。

3Yu Lu 和 Hugh Yu。“低雜訊 Silent Switcher μModule 和 LDO 穩壓器改善超聲雜訊和圖像品質.”模擬對話,第 56 卷,2022 年 4 月。

4“ADF4372: 集成 VCO 的微波寬頻合成器.”Analog Devices, Inc.,2021 年。

5雷·雷德利。“第二級 LC 過濾器設計。“ Switching Power 雜誌,2000 年 7 月。

6“AD9208: 14 位、3 GSPS、JESD204B、雙通道模數轉換器。“ Analog Devices, Inc.,2017 年。

7約翰·馬丁·德拉·克魯茲 (John Martin Dela Cruz) 和派翠克·帕薩奎安 (Patrick Pasaquian)。“優化信號鏈的電源系統—第2部分:高速數據轉換器。模擬對話,第 55 卷,2021 年 4 月

8Aldrick Limjoco、Patrick Pasaquian 和 Jefferson Eco。“Silent Switcher μModule 穩壓器可在一半的空間內安靜地為 GSPS 採樣 ADC 供電。“ Analog Devices, Inc.,2018 年。

作者簡介

黃星軒

undefined 2019 和 2021,分別集中在電力電子學上。 2019 年和 2021 年,分別專注於電力電子。

安馳科技 FAE support. Please e-mail

► Marketing.anstek@macnica.com

► 或加 安馳科技 LINE 洽詢

► 追蹤 安馳科技 Facebook

► 請加入 安馳YouTube頻道

► 立即填寫料號 申請樣品

洽詢更新產品、技術與安馳抽獎活動